## **THERMAL MODELING OF INTEGRATED CIRCUITS IN DIGITAL SIMULATION ENVIRONMENTS**

Vlad MOLEAVIN<sup>1</sup>, Ovidiu-George PROFIRESCU<sup>2</sup>, Marcel PROFIRESCU<sup>3</sup>

*The paper presents modeling and simulation methods for functional – thermal mixed simulation of digital integrated circuits. It presents the heat equation with several solving methods in simulation environments for digital circuits. Also, a simulation algorithm for functional – thermal behavior is described.*

**Keywords:** thermal, model, heat equation, digital circuits, Verilog

### **1. Introduction**

Currently, digital circuit design activities are grouped by several levels:

- Functional level design, using hardware description languages such as (Verilog, VHDL, SystemVerilog, SystemC, even C++);

- Schematics/netlist design using schematic tools or drawing tools. Gate level or transistor level design may be appropriate to achieve some area/timing requirements.

- Layout level design, where physical device geometry and interconnections are the result of the design process.

In all the above situations, functional simulation of the desired behavior is mandatory especially in case of complex logic. In this context, mixed functional – thermal simulation proposes a unified model for digital integrated circuits at the netlist level.

The netlist is a pure structural view of digital circuits<sup>(4)</sup>.

A simplified thermal behavior in digital circuits means heat generation and temperature dependency for some of the components parameters such as propagation delay.

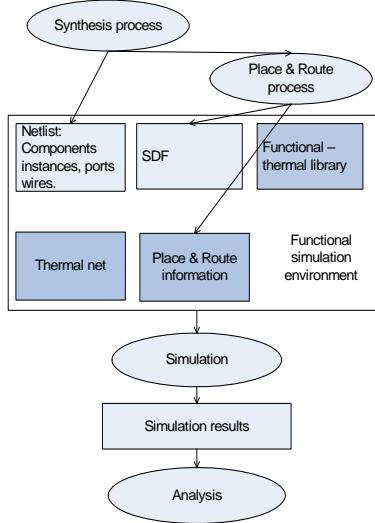

As shown in Fig. 1, Mixed Functional – Thermal simulation is derived from classical simulation process with additional thermal functionality. The simulation environment for mixes simulation uses as much as possible from

---

<sup>1</sup> Eng., Infineon Technologies Romania, e-mail: vlad\_moleavin@yahoo.com

<sup>2</sup> Eng., ON Semiconductor, Bucharest, Romania

<sup>3</sup> Eng., EDIL-Micro and Nanoelectronics R&D Centre of Excellence, University POLITEHNICA of Bucharest, Romania

<sup>4</sup> The netlist contains only basic digital components such as gates, flip-flops, latches, wires. It usually results from logic synthesis into a specific technology.

classical netlist simulation environments, for increasing efficiency and lowering the design effort.

Fig. 1 – Mixed Functional – thermal simulation flow (based on classical simulation environment)

The thermal model for digital circuits has two components: digital components thermal model (thermal generation) and thermal diffusion model of the entire silicon block. Together with the digital model they implement a functional loop that simulates digital circuits better in terms of timing, thermal behavior and power consumption.

## 2. Theoretical aspects

The *Thermal Net*[1] represents the circuit thermal model and encapsulates the diffusion model as well as geometrical information of each involved component. Together with the components' thermal model (thermal generation), the Thermal Net implements the overall thermal behavior. The main phenomena which govern the silicon thermal behavior are the heat generation and thermal diffusion. Other phenomena such as radiation and thermal convection are also involved. Both last effects are more and more important as the circuits dimension increases together with the consumed power.

In the context of thermal simulation for digital integrated circuits, the first two effects thermal generation and diffusion make a sufficient base to build a robust and flexible simulation environment.

The theory base for thermal behavior is represented by the heat equation and the consumed electrical power by digital components. The involved quantities used to model the thermal behavior of integrated circuits are:

- Thermal energy per volume unit.

- The generated thermal power by the individual digital components during normal function.

- The thermal flow exchanged by the discrete volume units as part of the discretized diffusion model.

Equation 1 represents the heat equation incorporating the above effects.

$$Cth * dT/dt = p\_gen + p\_diffusion = Iaverage\_V - kA * dT/dx \quad (1)$$

Where:

- $Iaverage$  is the average electrical current during the 'low to high' and 'high to low' transitions; to simplify the formulas, the average value was computed per time unit.

- $V$  is the VDD power voltage reference

- $k$  is the thermal conductivity

- $A$  is the area unit

- $Cth$  is the thermal capacity of Silicon per volume unit

Equation 2 shows the discretized form of the heat equation.

$$Cth * (T_{new} - T_{prev}) = Pd - k * A * ((T_{prev} - T_n)/dy + (T_{prev} - T_s)/dy + (T_{prev} - T_w)/dx + (T_{prev} - T_e)/dx) \quad (2)$$

Where:

- $T_{new}$  – the new temperature value of the current cell

- $T_{prev}$  – the current temperature value of the current cell

- $T_n$  – the north cell current temperature value

- $T_w$  – the west cell current temperature value

- $T_s$  – the south cell current temperature value

- $T_e$  – the east cell current temperature value

- $Pd$  – the dissipated power within the current cell (by the digital devices)

- $k$  – the thermal conductivity

- $A$  – the area unit

- $Cth$  – the thermal capacity of Silicon per volume unit

The left term represents the temperature variation per time unit in the current cell<sup>5</sup>.

The right term contains the generated power and exchanged heat with neighbor cells. The equation is bi-dimensional. The thermal capacity is computed as presented in Equation 3

---

<sup>5</sup> Discretization element

$$C_{th} = c * \rho * V \quad (3)$$

Where:

- $c$  is the Silicon specific heat

- $\rho$  is the Silicon density

- $V$  is the volume unit ( $dx * dy * dz$ )

An implicit method to solve the heat equation <sup>(6)</sup> uses the *Electrical-Thermal* analogy. Table 1 lists the involved quantities and their equivalence.

Table 1

Electrical and thermal dimensions analogy

| Electrical                           |            | Thermal                      |            |

|--------------------------------------|------------|------------------------------|------------|

| Parameter                            | Unit       | Parameter                    | Unit       |

| Electrical voltage (V)               | V          | Temperature (T)              | K          |

| Electrical current (I)               | $A = C/s$  | Heat flow (q)                | $W = J/s$  |

| Electrical conductivity ( $\sigma$ ) | $A/V * cm$ | Thermal conductivity (k)     | $W/K * cm$ |

| Electrical charge (Q)                | C          | Heat (H)                     | J          |

| Electrical resistance (R)            | $V/A$      | Thermal resistance ( $R_t$ ) | $K/W$      |

| Electrical capacity (C)              | $C/V$      | Thermal capacity ( $C_t$ )   | $J/K$      |

The thermal net is implemented by a RC net. The thermal flow is replaced by electrical currents and temperatures are computed as Voltages.

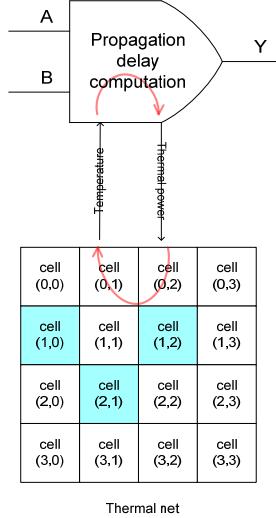

Digital components include the thermal generation in their functional model. Each digital device implement two additional virtual ports, **p** transmits the thermal power to the corresponding node in the thermal net and **T** receives the current temperature to be used in digital behavior model.

Fig. 2 shows the interface of a typical digital device with encapsulated thermal behavior. **P** and **T** can be implemented in Verilog as true ports or using the “resolution access<sup>(7)</sup>”

The components models are grouped into a thermal library that encapsulates all the components, models. A simulation library targets a specific technology.

Within a thermal library, each component model encapsulates both functional and thermal behaviors. More than this, the two models are linked, as shown in Fig. 2.

The digital circuit implemented by all its components constantly exchanges information with the associated thermal net. It injects thermal power in the thermal net nodes and retrieves the corresponding temperature values to adjust its components propagation delay values. Each component performs

<sup>6</sup> Is Electrical circuit RC equivalent equation.

<sup>7</sup> Each signal in design can be accessed by its hierarchical name

(top.module.submodule.signalname)

independently these actions. A functional loop is implemented between the two models. As a result the mixed environment is enriched in functionality.

Fig. 2 – Unified interface of a typical “thermal capable” device

It is possible to reveal malfunction because overheating or to estimate the thermal behavior. In some cases, temporary malfunction conditions may be highlighted, such as hold timing violations. In other cases the system may block because a timing error caused by overheating.

### 3. Thermal model implementation using Verilog Language in Modelsim based environments

A direct implementation for thermal net implements the discretized heat equation as Verilog functions into bi-dimensional structure. Each language has mechanisms (more or less efficient) to implement such an equation system.

Verilog supports real computation, functions and can be used to implement the most portable thermal net for digital simulation environments implemented in Verilog. Each thermal net cell is implemented by a set of signals, module instances, events and function calls. A special Verilog module will encapsulate the heat equation and temperature storage per volume unit. This is not be an efficient method as Verilog itself is an interpreted language<sup>8</sup>.

A more efficient way is to implement the thermal heavy computation in C and to link them somehow to the Verilog modules in simulation. Verilog provides

<sup>8</sup> It will be like simulate a machine to solve some computation instead solving them directly

a standard interface to C[3], called PLI<sup>(9)</sup>. Using such an implementation the heat equation is resolved by a C function and the thermal variables are also stored in C. The interaction between Verilog and C is triggered by Verilog events and shall be restricted as much as possible to increase simulation efficiency.

A particular environment using Modelsim on Windows platform, compiles the C code into a DLL<sup>(10)</sup> and loaded at runtime into the simulator. Standard methods are provided to access C functions.

A third method implies the usage of *Electrical – Thermal* analogy. The thermal net is modeled by a RC net which solves implicitly the heat equation. The analog devices Resistors and Capacitors can be modeled using an analog simulator coupled with the main digital simulator or using the recent Verilog[2] extension for analog devices<sup>(11)</sup>.

## 6. Conclusions

Adding thermal behavior to a digital circuit simulation increases the simulation accuracy in two of the most critical direction in complex systems design: timing estimation and thermal behavior. The closing loop between the two phenomena electrical and thermal allows digital simulations to catch malfunction conditions that are not pure digital but impact as much as a functional “bug”.

A possible implementation will follow the third method presented in the previous chapter. The discretized heat equation is implemented by a C function together with thermal data and thermal net structure. The thermal functionality is driven by the Verilog environment based on digital events.

A efficient simulation environment for mixed thermal and functional behavior will use as much as possible from a classic netlist simulation environment, will not modify the circuit itself and will introduce an additional simulation library for thermal components.

## R E F E R E N C E S

- [1] *K.Hofmann J.M.Karam T.Niculiu B.Courtois M.Glesner Vlad Moleavin.* Modelling and simulation of thermal effects on the system level. Therminic Conference, Grenoble, 1995

- [2] *Samir Palnitkar.* Verilog HDL - A Guide to Digital Design and Synthesis. SunSoft Press, 1996

- [3] *Stuart Sutherland.* The Verilog PLI Handbook. Springer, 1999

---

<sup>9</sup> Programming Language Interface – load a compile C structure and allow Verilog to access its members (variables and functions)

<sup>10</sup> Dynamic Linked Library

<sup>11</sup> Verilog posedă extensia VerilogA pentru modelarea circuitelor analogice simulate în mediul digital standard.