# SOURCE CURRENT-VOLTAGE LOOP BASED INSTANTANEOUS REACTIVE POWER THEORY CONTROL ALGORITHM BASED DSTATCOM FOR POWER QUALITY IMPROVEMENT

Muhammud Drak ALSEBAI<sup>1</sup>, N. KAMALA<sup>2</sup>

*Distribution Static Synchronous Compensator DSTATCOM is one of the custom power devices which is used to improve the power quality in the electrical grids. Instantaneous reactive power theory IRPT control algorithm is one of common control algorithm which is used to generate pulses for the IGBT/Diode switches of the voltage source inverter VSI of DSTATCOM device.*

*The effect of load apparent power increment on the working of DSTATCOM device with the traditional instantaneous reactive power theory control algorithm IRPT control algorithm is studied in this paper by using MATLAB simulation. The adding of source current-voltage loop SCVL to the traditional instantaneous reactive power theory control algorithm is done in this paper to improve the working of DSTATCOM device through the load apparent power increment and the results are reached through using the MATLAB simulation.*

**Keywords:** Distribution Static Synchronous Compensator DSTATCOM, Instantaneous Reactive Power theory IRPT control algorithm, Source current-voltage Loop SCVL, Source current-voltage Loop based Instantaneous Reactive Power theory SCVL\_IRPT control algorithm, Voltage Source Inverter VSI, Total harmonics distortion THD

## 1. Introduction

The passive filters are one of the common ways to compensate the reactive power in the distribution electrical grids. The main idea if these filters is to generate the reactive power needed by the load and to absorb the harmonics by making the impedance of the filter at the zero value toward a specific harmonic. One of the drawbacks of the passive filters that they have to be designed for a specific load and specific harmonics. [1]

The Static VAR compensator was widespread for the last three decades to compensate the reactive power and for the reducing of the flicker. It consists of thyristor-controlled reactor along with AC filters. The rate of the SVC is same rate of the load which is connected to. The drawback of SVC device that it can't be

<sup>1</sup> PhD Scholar, Dept. of Electrical Engineering, Jain (Deemed to Be University), Bangalore, India, e-mail: eng.muhammud.alsebai@gmail.com.

<sup>2</sup> PhD Associate Professor, Dept. of Robotics & Automation, Jain (Deemed to Be University), Bangalore, India, e-mail: kamalajai216@gmail.com

used when the power quality requirements of the distribution system require that the flicker improvement factor should be greater than two. [11]

Distribution Static Synchronous Compensator DSTACOM is dynamic compensator which can be applied for a different type of loads like unbalance loads, non-linear loads and rectified loads without the need to design a specific DSTATCOM to a specific load. The flicker improvement factor of DSTATCOM device is five and can be increased by increasing the rate of the DSTACOM device. One of the major challenges which face the DSTATCOM device is the control algorithm. The effective control algorithm should have the ability to drive the DSTATCOM device to respond for different power quality problems such as unbalance load, rectified load with harmonics, voltage sag, voltage fluctuation and load apparent power changing. There are many control algorithms to control DSTATCOM device. Instantaneous reactive power theory IRPT and synchronous reference frame are the most traditional and common control algorithms to drive the DSTATCOM device. [2] [11]

There are many criteria which make the DSTATCOM device the desirable device to improve the power quality in the distribution system. The emission limit is one of these criteria. For the low voltage system, the short-term flicker severity limit is  $Pst < 1$  and the long-term flicker severity is  $Plt < 0.65$ . The using of DSTATCOM device with arc furnace can improve the short-term flicker severity from  $Pst = 3.75$  without using of DSTATCOM to  $Pst = 0.76$  with DSTATCOM. The flicker improvement ratio, expressed as the ratio between the short-term flicker severity ( $Pst$ ) values without and with the compensating device, i.e.,  $FI = Pst_{\text{without}} / Pst_{\text{with}}$ , is around five when the compensating device is DSTATCOM device while it is around two when the compensating device is SVC with the same size and cost. [11]

This paper is focused on studying the response of DSTATCOM device based on instantaneous reactive power theory control algorithm due to the changing of load apparent power. This paper is suggested adding of source current-voltage loop to the mentioned control algorithm to improve its response toward the changing of the load apparent power and led the DSTATCOM device to be more reliable in this possible situation.

## 2. DSTATCOM DEVICE CONFIGURATION

### A. DSTATCOM device description

The three phases three wires DSTATCOM is used in this paper. The main functions of DSTATCOM device are to generate the reactive power which is needed by the load instead of the electrical source and led the source power factor to reach the unity value and to mitigate source current harmonics by monitoring the load current oscillation component and generating the compensating current

necessary to get rid of these oscillations which led to decrease the total harmonic distortion THD of the source current. [3]

The DSTATCOM device consists of three main parts: the dc energy storage and in this paper the dc capacitor is used; voltage source converter VSI which consists of six IGBT/Diode switches which they are opened and closed by the guiding of six signals generated by PWM device controlled by a control algorithm; and three interface inductances to get rid of the oscillation signals that occurs due to the working of the mentioned six switches. [3]

There are three important values which they are needed to be calculated while the designing procedures of DSTATCOM device: the capacity of the DC capacitor  $C_{dc}$ , the reference value of the capacitor dc voltage  $V_{dc}$  and the induction of the interface inductance  $L_f$ . [3]

### B. Design of the three phases three wires DSTATCOM Device

The simple design calculation of the three phases three wires DSTATCOM device which is able to compensate the load reactive power at the range rating of [1kVA-12kVA] at power factor of 0.8 is stated here in this paper. The reference dc bus voltage, dc bus capacitor, and interface inductor are calculated as follow:[3]

Table 1

DSTATCOM Device Parameters Calculations

| Magnitude | Formula                                                                                   | 1kVA<br>PF=0.8<br>1.47[A] | 4kVA<br>PF=0.8<br>5.8[A] | 8kVA<br>PF=0.8<br>11.5[A] | 12kVA<br>PF=0.8<br>17.1[A] |

|-----------|-------------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|----------------------------|

| $V_{dc}$  | $V_{dc} > [2 \times \sqrt{2} \times \frac{V_{LL}}{\sqrt{3}} \times m]$                    | 700[V]                    | 700[V]                   | 700[V]                    | 700[V]                     |

| $C_{dc}$  | $\frac{1}{2} C_{dc} [(V_{dc}^2) - (V_{dc1}^2)] = 3V(aI)t$                                 | 254[uF]                   | 1002[uF]                 | 1987[uF]                  | 2955[uF]                   |

| $L_f$     | $L_f = \frac{\sqrt{3} \times m \times V_{dc}}{12 \times a \times f_s \times i_{cr(p-p)}}$ | 114[mH]                   | 29[mH]                   | 14.6[mH]                  | 9.8[mH]                    |

where: m: is the modulation index and is considered as 1.

$V_{dc}$ : is the reference dc voltage;  $V_{dc}=700[V]$

$V_{dc1}$ : is the minimum voltage level of dc bus;  $V_{dc1}=697.5[V]$

a: is the over loading factor;  $a=1.2$

V: is the phase voltage;  $V=239.60$

I: is the phase current; depending on the load apparent power values and they are mentioned in the table above for each load.

t: is the time by which the dc bus voltage is to be recovered;  $t=350\mu S$ ;

$i_{cr(p-p)}$ : current ripple;  $i_{cr(p-p)} = 0.05 \times I$

$f_s$ : switching frequency;  $f_s=10[kHZ]$

The capacity of DC capacitor of the DSTATCOM device which is used in this paper is chosen to suit the load apparent power rate of 12[kVA] which is 3000[uF].

### 3. Source Current-Voltage Loop Based Instantaneous Reactive Power Theory Control Algorithm

The common instantaneous reactive power theory control algorithm uses one error signal as an input of hysteresis controller. This new control algorithm is used two error signals as an input for the hysteresis controller. The instantaneous reactive power theory algorithm is used to estimate the first error signals by comparing the compensating reference currents with the measured compensating currents generated by the DSTATCOM device. The second error signals are estimated by using source current-voltage loop which is compared the desired source reference currents with the measured source currents. Then these two error signals are passed through the hysteresis controller to generate the pulses for VSI switches in order to compensate the reactive power consumed by the load and to improve the power quality factor of the source to unity value.

#### A. Estimation of the first error signals by using common Instantaneous reactive power theory control algorithm

This control algorithm theory is estimated the compensating current reference of DSTATCOM device depending on the instantaneous active and reactive power of the load. It measures the active and reactive power of the load every second and estimates the reference compensating currents of the DSTATCOM device to generate the reactive power needed by load, to get rid of the oscillatory active power component caused by the rectified load.[4]

This control algorithm calculates the instantaneous active and reactive power of the load depending on the three phase voltages of the point of common coupling  $V_{PCC}$  and the three phase currents load  $I_{La}$ ,  $I_{Lb}$ ,  $I_{Lc}$  by using this equation:[4]

$$P = V_{\alpha} \times I_{\alpha} + V_{\beta} \times I_{\beta} \quad (1)$$

$$q = -V_{\beta} \times I_{\alpha} + V_{\alpha} \times I_{\beta} \quad (2)$$

$$\begin{bmatrix} P \\ q \end{bmatrix} = \begin{bmatrix} V_{\alpha} & V_{\beta} \\ -V_{\beta} & V_{\alpha} \end{bmatrix} \begin{bmatrix} I_{\alpha} \\ I_{\beta} \end{bmatrix} \quad (3)$$

The transfer from the abc coordinates to  $\alpha\beta$  coordinates for the three phase voltages of the point of common coupling and for the three phase currents of the load is needed. This transfer is needed to make the simulation process easier because it makes the zero-sequence of the load currents and the zero-sequence of the source voltages equal to zero and it is easy to deal with two variables more than three variables. This transfer can be done by using Clark transformation equations as mentioned in [4]

In order to keep the DC voltage of capacitor constant at the value of 700[V], the source need to provide the DSTATCOM device with power losses due to the switching process in IGBT/Diode switches. The  $P_{Loss}$  which is needed to be provided by the source can be estimated by using PI controller which

compare the reference DC voltage  $V_{dc}=700[V]$  with the measured  $V_{dc}$  voltage and give the error signal to the PI controller. The PI controller specification which is used in this paper is shown in the table below. [4]

Table 2

First PI Controller Specification

|                                   | Kp  | Ki |

|-----------------------------------|-----|----|

| First PI Controller Specification | 200 | 10 |

The estimation of reference compensating currents can be done by using the following equation:

$$I_{c\alpha}^* = \frac{1}{V_{\alpha}^2 + V_{\beta}^2} \times [(V_{\alpha} \times (P^* - P_{Loss})) + (-V_{\beta} \times q)] \quad (4)$$

$$I_{c\beta}^* = \frac{1}{V_{\alpha}^2 + V_{\beta}^2} \times [(V_{\beta} \times (P^* - P_{Loss})) + (V_{\alpha} \times q)] \quad (5)$$

In these equations the  $P^*$  and  $q$  are positive because they are needed to be compensated by the DSTATCOM device, while the  $P_{Loss}$  is negative because it is needed to be provided by the source as it is mentioned before. [4]

After the estimation of the compensating currents in  $\alpha\beta$  coordinates, it is needed to be transferred to the abc coordinates by using the inverse Clarke transformation as mentioned in [4]. The estimation of the first error signals can be done through the following equations

$$Err1a = I_{Ca}^* - I_{Ca\,m} \quad (6)$$

$$Err1b = I_{Cb}^* - I_{Cb\,m} \quad (7)$$

$$Err1c = I_{Cc}^* - I_{Cc\,m} \quad (8)$$

**B. Estimation of the second error signals by using source current-voltage loop:**

This control algorithm is used to estimate the reference source currents. The second error signals can be estimated by comparing the reference source currents with the measured source currents. [5]

The desired reference source currents should have the magnitude of  $I_{ap}$  which is necessary to keep the voltage of the dc capacitor at the rate of  $V_{dc}=700[V]$  and in the same phase of the source voltage waves to make the power factor of the source at the unity value. [5]

The magnitude of  $I_{ap}$  is estimated in this paper by using PI controller which is compared the reference DC voltage of capacitor  $V_{dc\_ref}=700[V]$  with the measured dc voltage of the capacitor and has the specification as shown in the table below. [5]

Table 3

Second PI Controller Specification

|                                    | Kp   | Ki |

|------------------------------------|------|----|

| Second PI Controller Specification | 0.56 | 10 |

While the phase of the source voltage waves can be granted by multiplying the I<sub>ap</sub> magnitude with the p.u source voltage waves. The p.u. voltage waves can be achieved by dividing the source voltage waves by the source voltage peak values for each phase. To make the source current waves with the same phase with source voltage waves the DSTATCOM device will generate the compensating currents to provide the load with needed reactive power and that will make the reactive power which is provided by the source at zero value. The source reference currents for this control algorithm are given by equations below:[5]

$$I_{Sa}^* = I_{ap} \times V_{a_{p.u.}} = I_{ap} \sin \omega t \quad (8)$$

$$I_{Sb}^* = I_{ap} \times V_{b_{p.u.}} = I_{ap} \sin(\omega t - 120^\circ) \quad (9)$$

$$I_{Sc}^* = I_{ap} \times V_{c_{p.u.}} = I_{ap} \sin(\omega t + 120^\circ) \quad (10)$$

The estimation of the second error signals can be done through the following equations

$$Err2a = I_{Sa}^* - I_{Sa\_m} \quad (11)$$

$$Err2b = I_{Sb}^* - I_{Sb\_m} \quad (12)$$

$$Err2c = I_{Sc}^* - I_{Sc\_m} \quad (13)$$

### C. Hysteresis current controller

This hysteresis controller is used to generate the pulses for the 6 IGBT/Diode switches of the DSTATCOM device in this paper. The input signals of this controller are the first error signals which are generated by the instantaneous reactive power theory control algorithm and the second error signals which are generated by the added source current-voltage loop. [6]

The important parameter in the hysteresis controller is the hysteresis bandwidth  $h$  which is 3% in this paper and this value will make the switching frequency variation to be 10[kHZ]. The error signals are compared with the hysteresis band width. If the error signals of the phase a  $err_a = err_{a1} + err_{a2}$  signals are greater than  $h+$  the hysteresis controller will generate a pulse for the first IGBT/Diode switch S1 in the phase a leg of DSTATCOM device. While when the error signals of the phase a  $err_a = err_{a1} + err_{a2}$  signals are lower the  $h-$  the hysteresis controller will generate a pulse for the second IGBT/Diode switch S2 in the phase a leg of DSTATCOM device. [6]

## 4. Simulation and Results

The simulation process is taken place in MATLAB R2021a. The solver which is used in this simulation is ODE45 with simulation type of Discrete and sample time of 10e-5 [s]. The electrical grid contains of real electrical source, shunt DSTATCOM device to improve the power quality, DSTATCOM controller

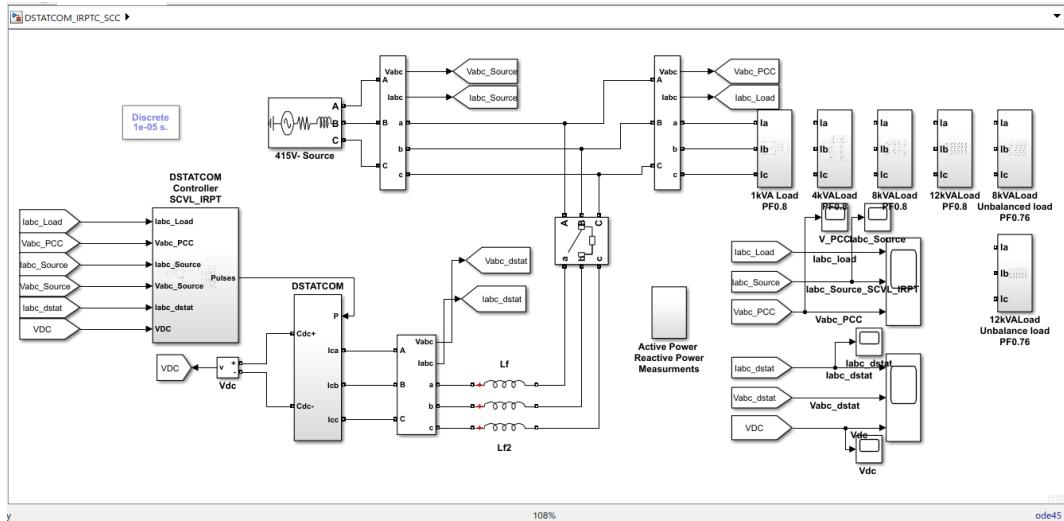

to generate the pulses needed for DSTATCOM switches and rectified non-linear load. The Electrical source specification is voltage phase to phase RMS of 415[V] with internal impedance of  $r_s=0.02[\Omega]$  and  $L_s=2[mH]$ . DSTATCOM Device rating is up to 12[kVA] and consists of 6 IGBT/Diode switches, capacitor with capacity of 3000[uF] and DC voltage rate of  $V_{dc}=700[V]$  and interface inductance  $L_f= [100-40-17-12] [mH]$  depending on the apparent power of the load. See Fig.1:

Fig. 1. System grid with 415v electrical source, 1kVA/4kVA/8kVA/12kVA PF=0.8 balanced rectified non-linear loads, 8kVA/12kVA PF=0.76 unbalanced rectified non-linear loads and shunt DSTATCOM Device for improving the power quality

The rectified non-linear load apparent power ratings which are used in this simulation are balanced load [1kVA – 4kVA – 8kVA -12kVA] with PF=0.8 and unbalanced load [8kVA – 12kVA] with PF=0.76. The PF=0.76 and PF=0.8 are chosen because the vast majority of the loads which spread disturbances in the distribution system are factorial loads such as arc furnaces with power factor of 0.7-0.8. The 1[kVA] with PF=0.8 load consists of rectifier connected to resistance  $R=1000[\Omega]$  which consumes  $P=320[W]$  in parallel with non-linear load which consumes  $P=480[W]$   $q=600[VAr]$  so the total load is  $P=800[W]$   $q=600[VAr]$ . While the 4[kVA] consists of 4 of 1[kVA] loads which are connected in parallel and so on for the other loads 8[kVA] and 12[kVA].

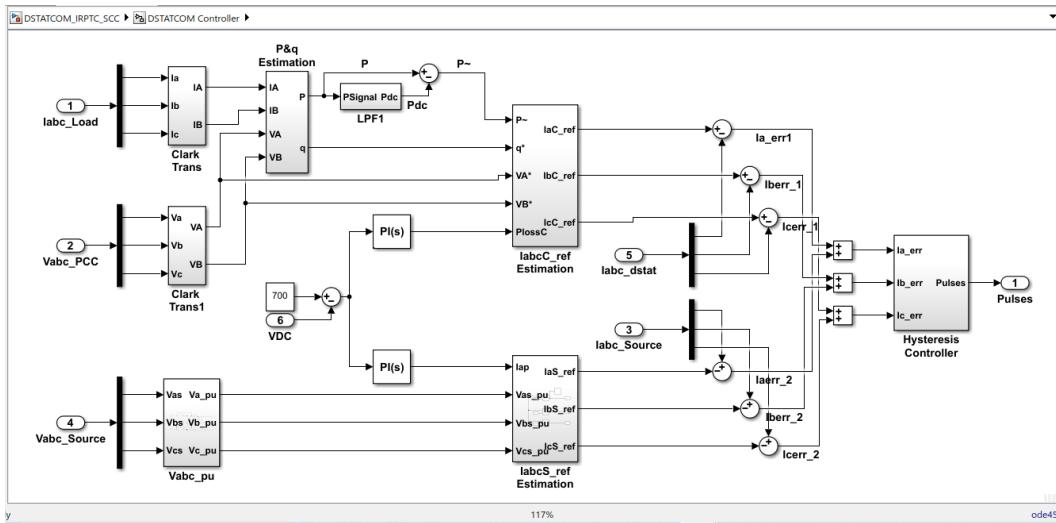

Fig. 2. Source current-voltage loop based instantaneous reactive power theory control algorithm

The control algorithms which are used in this simulation to control the DASTACOM device are Instantaneous Reactive Power Theory control algorithm IRPT and source current-voltage loop based Instantaneous Reactive Power Theory control algorithm SCVL\_IRPT. The results of source active power, source reactive power, source power factor and total harmonic distortion THD of source current wave have taken for three situations which they are electrical grid without connecting DSATACOM device, electrical grid with connecting DSTATCOM device with IRPT control algorithm and electrical grid with connecting DSTATCOM device with SCVL\_IRPT control algorithm at balanced rectified non-linear load with apparent power of [ 1kVA – 4kVA – 8kVA – 12kVA] at power factor of 0.8 and unbalanced load rectified non-linear load with apparent power of [8kVA – 12kVA] at power factor of 0.76. These results show the effect of the increment of the load apparent power on the DSTATCOM device working for the two types of control algorithms which are used in this simulation. See Fig.2. The comparison of the results is done to show if the adding of source current-voltage loop to Instantaneous reactive power theory control algorithm will improve the DSTATCOM device working at the increment of the load apparent power ratings.

#### A. Balanced Rectified non-linear load with apparent power of 1[kVA]

The results show that connecting of DSTATCOM device with IRPT control algorithm improves the THD of source current wave from 9.40% to 3.35% and improves the PF of the electrical source from 0.8 to 0.99. while the connecting of DSTATCOM device with SCVL\_IRPT control algorithm improves the THD of source current wave from 9.40% to 3.23% and improves the PF of the electrical source from 0.8 to 0.99.

The adding of SCVL to control algorithm improves the DSTATCOM device working on mitigation of harmonics in a small margin from 3.35% to 3.23% while the same power factor of 0.99 is granted from both ways of control algorithms at the load apparent power rating of 1[kVA].

Table 4

**Results at Balanced Rectified non-linear Load 1[kVA]**

| Rectified non-linear Load, 1[kVA], PF=0.8, THD= 9.40%, Lf=100[mH] |                          |                              |                 |                         |

|-------------------------------------------------------------------|--------------------------|------------------------------|-----------------|-------------------------|

|                                                                   | Source Active power P[W] | Source Reactive power Q[VAr] | Power Factor PF | Source current wave THD |

| Without                                                           | 800                      | 600                          | 0.8             | 9.40%                   |

| IRPT                                                              | 817                      | 3.6                          | 0.99            | 3.35%                   |

| SCVL_IRPT                                                         | 817                      | 3                            | 0.99            | 3.23%                   |

**B. Balanced Rectified non-linear load with apparent power of 4[kVA]:**

Table 5

**Results at Balanced Rectified non-linear Load 4[kVA]**

| Rectified non-linear Load, 4[kVA], PF=0.79, THD= 9.00%, Lf=40[mH] |      |        |      |       |

|-------------------------------------------------------------------|------|--------|------|-------|

|                                                                   | P[W] | Q[VAr] | PF   | THD   |

| Without                                                           | 3150 | 2424   | 0.79 | 9.00% |

| IRPT                                                              | 3230 | 20     | 0.99 | 3.91% |

| SCVL_IRPT                                                         | 3240 | 26     | 0.99 | 3.71% |

The results show that connecting of DSTATCOM device with IRPT control algorithm improves the THD of source current wave from 9.00% to 3.91% and improves the PF of the electrical source from 0.79 to 0.99. while the connecting of DSTATCOM device with SCVL\_IRPT control algorithm improves the THD of source current wave from 9.00% to 3.71% and improves the PF of the electrical source from 0.8 to 0.99. The adding of SCVL to control algorithm improves the DSTATCOM device working on mitigation of harmonics in a small margin from 3.91% to 3.71% while the same power factor of 0.99 is granted from both ways of control algorithms at the load apparent power rating of 4[kVA].

**C. Balanced Rectified non-linear load with apparent power of 8[kVA]:**

Table 6

**Results at Balanced Rectified non-linear Load 8[kVA]**

| Rectified non-linear Load, 8[kVA], PF=0.78, THD= 8.64%, Lf=17[mH] |      |        |      |       |

|-------------------------------------------------------------------|------|--------|------|-------|

|                                                                   | P[W] | Q[VAr] | PF   | THD   |

| Without                                                           | 6180 | 4800   | 0.78 | 8.64% |

| IRPT                                                              | 6400 | 50     | 0.99 | 4.61% |

| SCVL_IRPT                                                         | 6450 | 40     | 0.99 | 3.74% |

The results show that connecting of DSTATCOM device with IRPT control algorithm has improves the THD of source current wave from 8.64% to 4.61% and has improves the PF of the electrical source from 0.79 to 0.99. while the connecting of DSTATCOM device with SCVL\_IRPT control algorithm

improves the THD of source current wave from 9.00% to 3.74% and improves the PF of the electrical source from 0.8 to 0.99.

The adding of SCVL to control algorithm improves the DSTATCOM device working on mitigation of harmonics from 4.61% to 3.74% with margin of 0.9% while the same power factor of 0.99 is granted from the both ways of control algorithms at the load apparent power rating of 8[kVA]. The margin of harmonic mitigation 0.9% between the two control algorithms increases at the load apparent power rating of 8[kVA] in comparison with margin of harmonic mitigation 0.2% between the two control algorithms at the previous two load apparent power ratings 1[kVA] and 4[kVA].

**D. Balanced Rectified non-linear load with apparent power of 12[kVA]:**

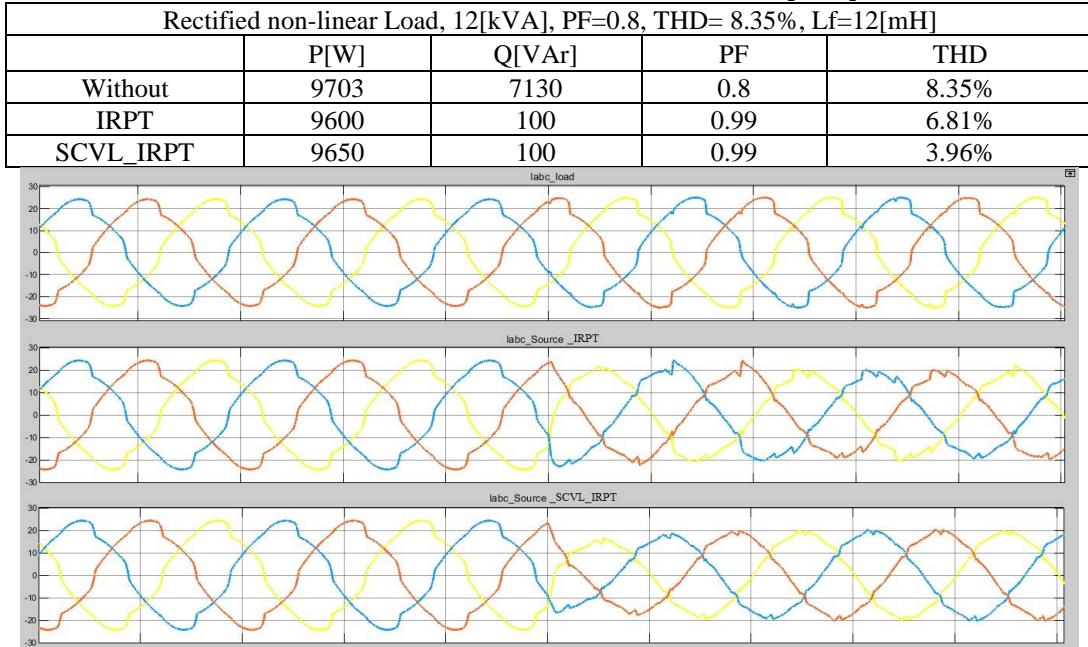

Table 7

**Results at Balanced Rectified non-linear Load 8[kVA]**

Fig. 3. Three phase current load wave, three phase currents source wave while the using IRPT control algorithm only and THD of the source current wave is 6.81% after compensation, three phase currents source wave while the using of SCVL\_IRPT control algorithm and THD of the source current wave is 3.96% after compensation at the 12[kVA] PF=0.8 balanced rectified non-linear load

The results show that connecting of DSTATCOM device with IRPT control algorithm improves the THD of source current wave from 8.35% to 6.81% and improves the PF of the electrical source from 0.8 to 0.99. while the connecting of DSTATCOM device with SCVL\_IRPT control algorithm improves the THD of source current wave from 8.35% to 3.96% and improves the PF of the electrical source from 0.8 to 0.99. The margin of harmonics mitigation between

the two control algorithms increases from 0.9% at the load apparent power 8[kVA] to 2.85% at the load apparent power 12[kVA]. Fig.3 shows the source current waves when DSTATCOM device with IRPT control algorithm is used, the source current waves when DSTATCOM device with the SCVL\_IRPT control algorithm is used. The DSTATCOM device is connected at the  $t=0.2[\text{S}]$ . It shows that before the compensation process the source current wave is deformed and away from the sinusoidal shape because the THD rate is 8.64%. It returns into the sinusoidal shape after compensation process by DSTATCOM device. The source current wave when the SCVL\_IRPT control algorithm is used is near to sinusoidal form more than the traditional IRPT control algorithm.

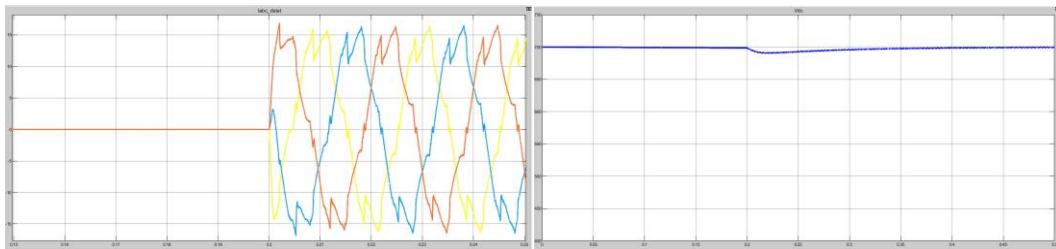

Fig. 4. DSTACOM compensating current at the 12[kVA] PF=0.8 balanced rectified non-linear load while the using of SCVL\_IRPT control algorithm, PI controller keep the Vdc of the capacitor constant at 700[V] at the 12[kVA] PF=0.8 balanced rectified non-linear load while the using of SCVL\_IRPT control algorithm.

Fig.4 shows the compensating current at the 12[kVA] PF=0.8 rectified non-linear load which generated by DSTATCOM device to mitigate the harmonics and compensate the reactive power of the load. In order to reach that the control algorithm should keep the DC voltage of the DSTATCOM capacitor at constant rate of 700[V] as shown in Fig.4.

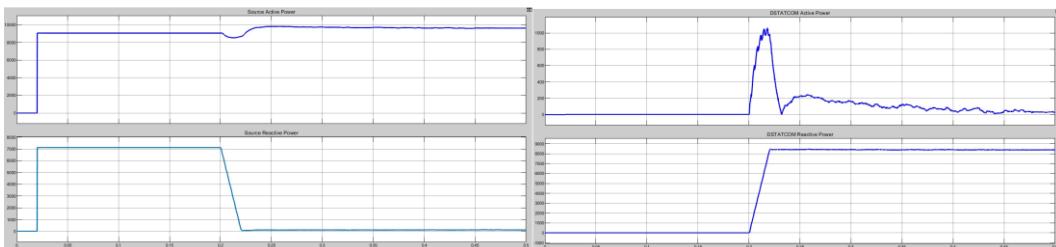

Fig. 5. Source active and reactive power before and after compensation at the 12[kVA] PF=0.8 balanced rectified non-linear load while the using of SCVL\_IRPT control algorithm, DSTATCOM active and reactive power before and after compensation at the 12[kVA] PF=0.8 balanced rectified non-linear load while the using of SCVL\_IRPT control algorithm.

The DSTATCOM device purpose is to compensate the reactive power of the load and let the source to provide the load with the active power only which is lead to a source unity power factor. Fig.5 shows that before the compensation process the source was providing the load with reactive power of 7130[VAr] but

after compensation process at the  $t=0.2$  the reactive power generated by the source become only 100[VAr] which is lead to power factor of 0.99. Fig.5 shows that the reactive power which is generated by the DSTATCOM before compensation process is almost zero but after the compensation process at  $t=0.2$  it becomes 8400[VAr] which is enough to cover all the reactive power of the load and lead the reactive power provided by source to become 100[VAr].

**E. Unbalanced Rectified non-linear load with apparent power of 8[kVA]:**

The unbalanced load is reached by using the following three impedances in each phase  $Z_a=1+j3.2$ ,  $Z_b=2+j6.4$ ,  $Z_c=3+j9.6$

Table 8

**Results at Unbalanced Rectified non-linear Load 8[kVA]**

| Unbalanced Rectified non-linear Load, 8[kVA], PF=0.76, THD= 7.79%, Lf=17[mH] |      |        |      |       |

|------------------------------------------------------------------------------|------|--------|------|-------|

|                                                                              | P[W] | Q[VAr] | PF   | THD   |

| Without                                                                      | 5400 | 4500   | 0.76 | 7.97% |

| IRPT                                                                         | 5580 | 50     | 0.99 | 5.68% |

| SCVL_IRPT                                                                    | 5670 | 70     | 0.99 | 3.50% |

The results show that connecting the DSTATCOM device with IRPT control algorithm improves THD of the source current wave from 7.97% before connecting the DSTATCOM device to 5.68%, improves the Power factor of the source current wave from 0.76% to 0.99% and improves the source current wave from unbalanced shape  $V_a_m=15.5[V]$   $V_b_m=14.5[V]$   $V_c_m=13.5[V]$  to balanced shape  $V_a_m=12[V]$   $V_b_m=11.8[V]$   $V_c_m=11.8[V]$ . The results show that connecting the DSTATCOM device with SCVL\_IRPT control algorithm improves THD of the source current wave from 7.97% before connecting the DSTATCOM device to 3.50%, improves the Power factor of the source current wave from 0.76% to 0.99% and improves the source current wave from unbalanced shape  $V_a_m=15.5[V]$   $V_b_m=14.5[V]$   $V_c_m=13.5[V]$  to balanced shape  $V_a_m=11.5[V]$   $V_b_m=11.6[V]$   $V_c_m=10.8[V]$

The using of DSTATCOM with SCVL\_IRPT control algorithm is better than IRPT control algorithm with unbalanced rectified load at power apparent of 8[kVA]. Even though the DSTATCOM Device with IRPT makes the load more balanced than SCVL\_IRPT control algorithm, but the using of SCVL\_IRPT control algorithm makes the source current THD at the acceptable rate in comparison with IRPT control algorithm.

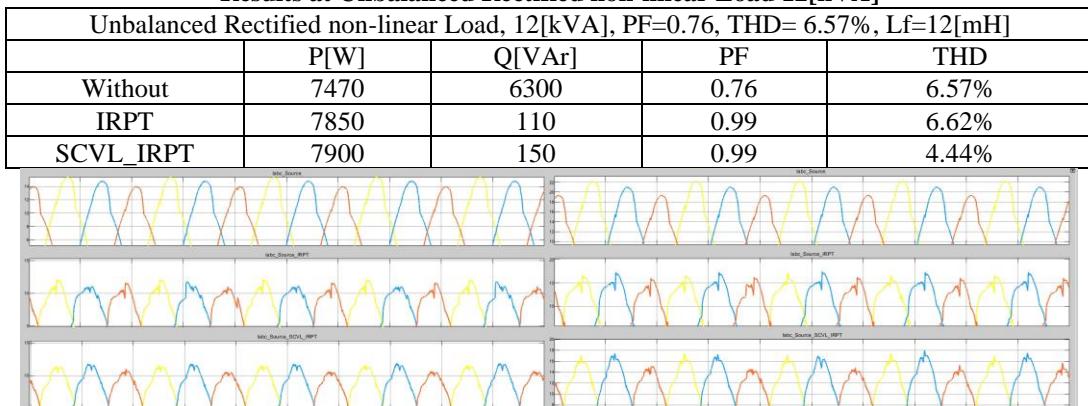

**F. Unbalanced Rectified non-linear load with apparent power of 12[kVA]:**

The unbalanced load is reached by using the following three impedances in each phase  $Z_a=1+j3.2$ ,  $Z_b=2+j6.4$ ,  $Z_c=3+j9.6$

The results show that connecting the DSTATCOM device with IRPT control algorithm kept THD of the source current wave around 6.57%, improves the Power factor of the source current wave from 0.76% to 0.99% and improves

the source current wave from unbalanced shape  $V_a_m=22[V]$   $V_b_m=21[V]$   $V_c_m=19[V]$  to balanced shape  $V_a_m=16.5[V]$   $V_b_m=17[V]$   $V_c_m=16.4[V]$

The results show that connecting the DSTATCOM device with SCVL\_IRPT control algorithm improves THD of the source current wave from 6.75% before connecting the DSTATCOM device to 4.44%, improves the Power factor of the source current wave from 0.76% to 0.99% and improves the source current wave from unbalanced shape  $V_a_m=22[V]$   $V_b_m=21[V]$   $V_c_m=19[V]$  to balanced shape  $V_a_m=16.3[V]$   $V_b_m=16.5[V]$   $V_c_m=15.3[V]$

The using of DSTATCOM with SCVL\_IRPT control algorithm is better than IRPT control algorithm with unbalanced rectified load at power apparent of 8[kVA]. Even though the DSTATCOM Device with IRPT makes the load more balanced than SCVL\_IRPT control algorithm, but the using of SCVL\_IRPT control algorithm makes the source current THD at the acceptable rate in comparison with IRPT control algorithm.

Table 9

Results at Unbalanced Rectified non-linear Load 12[kVA]

Fig. 6. Three Phase source currents load without DSTATCOM, Three phase source currents load with DSTATCOM with IRPT controller, Three phase source currents load with DSTATCOM with SCVL\_IRPT controller at unbalanced rectified load with power apparent of [8-12] [kVA]

PF=0.76%

#### 4. Comparison with the relevant studies:

The instantaneous reactive power theory is used to control DSTATCOM device with the unbalance rectified load. The error signals are estimated by comparing the reference compensating currents with the measured currents instead of comparing the reference source currents with the measured source currents in order to make it suitable for unbalanced load. The apparent power of the unbalanced load is around 2[kVA]. The maximum power of the DSTATCOM device is 12[kVA].[7]

The source current voltage algorithm is used to control active filter with balanced rectified load. The fuzzy logic controller is used instead of PI controller to estimate the amplitude of source referent currents and compare them with the sensed source currents to generate the error signals. The apparent power of the balanced load is around 6[kVA]. The maximum power of the DSTATCOM device is more than 12[kVA].[5]

The instantaneous reactive power theory is used to control the shunt active filter to improve the power quality of the brushless DC motor. The sliding mode control is used instead of PI controller estimate the power loss which is used to estimate the reference compensating currents to compare them with the sensed compensating currents to find the error signals. The apparent power of the balanced load is around 8[kVA]. The maximum apparent power of the DSTATCOM is 8[kVA].[4] The synchronous reference frame is used to control the DSTATCOM to correct the voltage sag with balanced load. The apparent power of the balanced load is around 4[kVA]. The maximum apparent power of the DSTATCOM device is 24[kVA].[6] The instantaneous reactive power theory is used to control the DSTATCOM Device to improve the power quality of the distribution system. Five artificial neural networks are used instead of the PI controller and low pass filters in the control algorithm. The input matrixes and output matrixes to train the five artificial neural networks are extracted from applying the conventional control algorithm. The simulation done for different situation of unbalanced voltage source (amplitudes and phases). The apparent power of the load is 20[kVA]. The maximum power of the DSTATCOM device is 28[kVA].[8] The synchronous reference frame is used to control the DSTACOM device to improve the power quality of the hospital load. The interval type 2 fuzzy logic controller is used instead of PI controller and the recursive least square filter is used instead of low pass filter to help generating the error signals. The apparent power of the hospital load is 30[kVA]. The maximum apparent power of the DSTATCOM device is 50[kVA]. [9] The ADALINE control algorithm is used to control the DSTATCOM device to improve the power quality of the balanced linear and non-linear load. The apparent power of the balanced load is 0.3[kVA]. The maximum apparent power of the DSTATCOM device is 12[kVA]. [10]

This paper is used the combined of two conventional controllers. The instantaneous reactive power theory along with the source current voltage loop are used to extract the error signals. The apparent power of the load is 12[kVA]. The maximum apparent power of the DSTATCOM device is 12[kVA]. This paper is aimed to find a control algorithm which improves the efficiency of DSTATCOM device with balanced and unbalanced load when the apparent power of the load is near to maximum apparent power of the DSTATCOM device.

## 5. Conclusion

The simulation of DSTATCOM device with two control algorithm instantaneous reactive power theory IRPT control algorithm and source current-voltage loop based instantaneous reactive power theory SCVL\_IRPT control algorithm is done and the effect of increment of load apparent power on DSTATCOM device with two control algorithms is studied in this paper. The increment of load apparent power has no effect on improving the source power factor PF with DSTATCOM device with both of two control algorithms which stays constant from approximately 0.8-0.76 before compensation to 0.99 after compensation for balanced and unbalanced load respectively. It means that the DSTATCOM device after compensation with the two control algorithms provides the load with the necessary reactive power and makes the reactive power which is provided by the electrical source to be near the zero value and that leads the source power factor to be near the unity value.

On the other hand, the increment of load apparent power affects the DSTATCOM harmonics mitigation with the instantaneous reactive power theory control algorithm when the load apparent power reaches the DSTATCOM apparent power rate of 12[kVA] for balanced and unbalanced load. The results show that total harmonics distortion increases from 3.35% at the load apparent power of balanced 1[kVA] PF=0.8 to 6.81% at the load apparent power of balanced 12[kVA] PF=0.8 and increases from 5.68% at the load apparent power of unbalanced 8[kVA] PF=0.76 to 6.62% at the load apparent power of unbalanced 12[kVA] PF=0.76. While the increment of the load power apparent doesn't affect that much the DSTACOM harmonics mitigation with the source current-voltage loop based instantaneous reactive power theory control algorithm when the load apparent power reaches the DSTATCOM apparent power rate of 12[kVA] for balanced and unbalanced load. The results show that total harmonics distortion increases from 3.23% at the load apparent power of balanced 1[kVA] PF=0.8 to 3.96% only at the load apparent power of balanced 12[kVA] PF=0.8 and increases from 3.50% at the load apparent power of unbalanced 8[kVA] PF=0.76 to 4.44% at the load apparent power of unbalanced 12[kVA] PF=0.76 which means it stays somehow constant. As a result, the paper shows that adding of source current-voltage loop to the traditional instantaneous reactive power theory control algorithm plays an important role in increasing the efficiency of DSTATCOM device in current harmonics mitigation regarding the increment of the load apparent load. Hence it can be concluded that the SCVL\_IRPT control algorithm is effective in controlling DSTATCOM device with the balance and unbalance loads which the apparent load power of them is near to the maximum apparent load power rate of the DSTATCOM Device.

## R E F E R E N C E S

- [1]. Gajendra Singh Chawda, Abdul Gafoor Haik, Om Prakash Mahela, Sanjeevikumar Padmanaban, Jens Bo Holm-Nielsen, 'Comprehensive Review of Distributed FACTS Control Algorithms for Power Quality Enhancement in Utility Grid with Renewable Energy Penetration' DOI10.1109/ACCESS.2020.3000931, IEEE Access, p.22, 2020

- [2]. Hirofumi Akagi, Yoshihira Kanazawa, Akira Nabae, 'Instantaneous Reactive Power Compensators Comprising Switching Devices without Energy Storage Components' IEEE Transactions on Industry Applications, Vol. IA-20, No. 3, p.p. 625-630 May/June 1984

- [3]. Bhim Singh, P. Jayaprakash, D. P. Kothari, Fellow, Ambrish Chandra, Kamal Al Haddad, 'Comprehensive Study of DSTATCOM Configurations' IEEE Transactions on Industrial Informatics, Vol. 10, No. 2, p.p. 854-870, May 2014

- [4]. S. Kumaresan, H. Habeebullah Sait, 'Design and control of shunt active power filter for power quality improvement of utility powered brushless DC motor drives' Automatika Journal for Control, Measurement, Electronics, Computing and Communications, VOL. 61, NO. 3, p.p. 507-521, 2020

- [5]. Kishore Kumar Pedapenki, S.P.Gupta, Mukesh Kumar Pathak, 'Comparison of PI & Fuzzy Logic Controller for Shunt Active Power Filter' 2013 IEEE 8th International Conference on Industrial and Information Systems, ICIIS 2013, pp.42-47, Aug. 18-20, 2013, Sri Lanka

- [6]. Vikas Purushothaman, Bobin K Mathew, 'Voltage Sag Correction in Distribution System Using DSTATCOM with PI and Hysteresis Controllers', International Conference on Magnetics, Machines & Drives (AICERA-2014 iCMMD), IEEE, 2014

- [7]. Sharad S.Pawar, A.P.Deshpande, Meera Murali, 'Modelling and Simulation of DSTATCOM for Power Quality Improvement in Distribution System Using MATLAB Simulink Tool', 2015 International Conference on Energy Systems and Applications (ICESA 2015), pp. 224-227, 30 Oct - 01 Nov, 2015, Pune, India.

- [8]. J. Jayachandran, R. Murali Sachithanandam 'Neural Network-Based Control Algorithm for DSTATCOM Under Nonideal Source Voltage and Varying Load Conditions', CANADIAN JOURNAL OF ELECTRICAL AND COMPUTER ENGINEERING, VOL. 38, NO. 4, FALL 2015, pp. 307-317, FALL 2015

- [9]. SATHISH BABU PANDU, C. K. SUNDARABALAN, N. S. SRINATH, T. SANTHANA KRISHNAN, G. SOORYA PRIYA, C. BALASUNDAR, JAYANT SHARMA, G. SOUNDARYA, PIERLUIGI SIANO AND HASSAN HAES ALHELOU, 'Power Quality Enhancement in Sensitive Local Distribution Grid Using Interval Type-II Fuzzy Logic Controlled' DSTATCOM', IEEE ACCESS, VOLUME 9, 2021, Digital Object Identifier 10.1109/ACCESS.2021.3072865, pp. 59888- 59899, April 26, 2021.

- [10]. Soumya Mishra, Soumya Mishra, Pavan Kalyan M, Sreejith R; Spoorthi M L and Hemalatha J G, 'A Comparative Study Of ILST and ANN Algorithm for Control of DSTATCOM', 2021 International Conference on Design Innovations for 3Cs Compute Communicate Control (ICDI3C), pp.45-50, June 2021, Bangalore, India

- [11]. Working Group B4.19, Edited by Dr I Arslan Erinmez, 'STATIC SYNCHRONOUS COMPENSATOR (STATCOM) FOR ARC FURNACE AND FLICKER COMPENSATION', Report presented at the request of the Chairmen of Study Committee B4, Marcio Szechtman/ Prof Dr Dusan Povh, CIGRE, p. 170, December 2003